参考

《计算机组成与设计》

计算机概要与技术

计算机系统结构中的8大伟大思想

- 摩尔定律

- 抽象简化设计

- 加速大概率事件

- 通过并行提高性能

- 通过流水线提高性能

- 通过预测提高性能

- 存储器层次

- 通过冗余提高性能

处理器

处理器从逻辑上包括两个主要部件:数据通路和控制器

- 数据通路 执行算术操作

- 控制器 指导数据通路、存储器和I/O设备按照程序的指令正确执行

数据安全

内存是程序运行时的存储空间,用于保存程序运行时所使用的数据,内存由

DRAM芯片组成,DRAM是dynamic random access memory的缩写,无论数

据存储在什么位置,DRAM访问内存的时间基本相同。缓存是一种小而快的存

储器,一般作为DRAM的缓冲,缓存使用静态随机访问存储器SRAM,全称是

Static Random Access Memory

- 易失性存储器 类似DRAM的存储器,仅在加电时保存数据,也称主存储器,

内存是靠电平来保存数据的,一旦断电数据就会丢失 - 非易失性存储器 在掉电时仍可保持数据的存储器,例如磁盘、闪存光盘

(CDROM, DVD),是靠磁性来保存数据的,断电不会影响数据

早期DRAM在主存储器中占主导地位,而磁盘在二级存储器中占主地位,后来

非易失性半导体存储器–闪存在个人移动设备中替代了磁盘,比如手机宣传

8+128G,8就是指手机内存,128G就是手机闪存,相当于电脑的磁盘

接口

性能

- 响应时间 也叫执行时间,是计算机完成某任务所需的总时间,包括硬盘

访问、内存访问、I/O活动、操作系统开销和CPU执行时间 - 吞吐率 也叫带宽,性能的另一种度量参数,表示单位时间内完成的任务

数量 - X是Y的n倍快 性能X/性能Y=n=执行时间Y/执行时间X

性能的度量

- CPU执行时间 只表示在CPU上花费的时间,可以细分为用于用户程序的时

间和操作系统为用户服务花去的CPU时间。前者称为用户CPU时间,后者称为

系统CPU时间 - 时钟周期 为计算机一个时钟周期的时间,通常是处理器时钟

- 时钟长度 每个时钟周期持续的时间长度

- 一个程序的CPU执行时间=一个程序的CPU时钟周期数*时钟周期时间

指令的性能

指令数:执行某程序所需的总指令数量

- CPU时钟周期数=程序的指令数*每条指令的平均时钟周期数

- CPI 表示执行每条指令所需的时钟周期数的平均值,不同的指令需要的时间

可能不同,CPI是所有指令所用时钟周期数的平均值 - CPU时间=指令数*CPI/时钟频率

Amdahl

改进后的执行时间=受改进影响的执行时间/改进量+不受影响的执行时间

MIPS

MIPS=指令数/(执行时间*10^6) 指令执行的频率

计算机的语言

目前有四种流行的指令集,接下来会介绍MIPS指令架构

- ARMv7

- Intel x86

- ARMv8

- MIPS

操作数

32个64bit的寄存器文件,每个地址都是由8位地址符表示也就是字节编址,

使用大端法表示,一个字是32位

汇编语言

- 加法 dadd $r1,$r2,$r3 $r1=$r2+$r3

- 减法 dsub $r1,$r2,$r3 $r1=$r2-$r3

- 立即数加法 daddi $r1,$r2,20 $r1=$r2+20

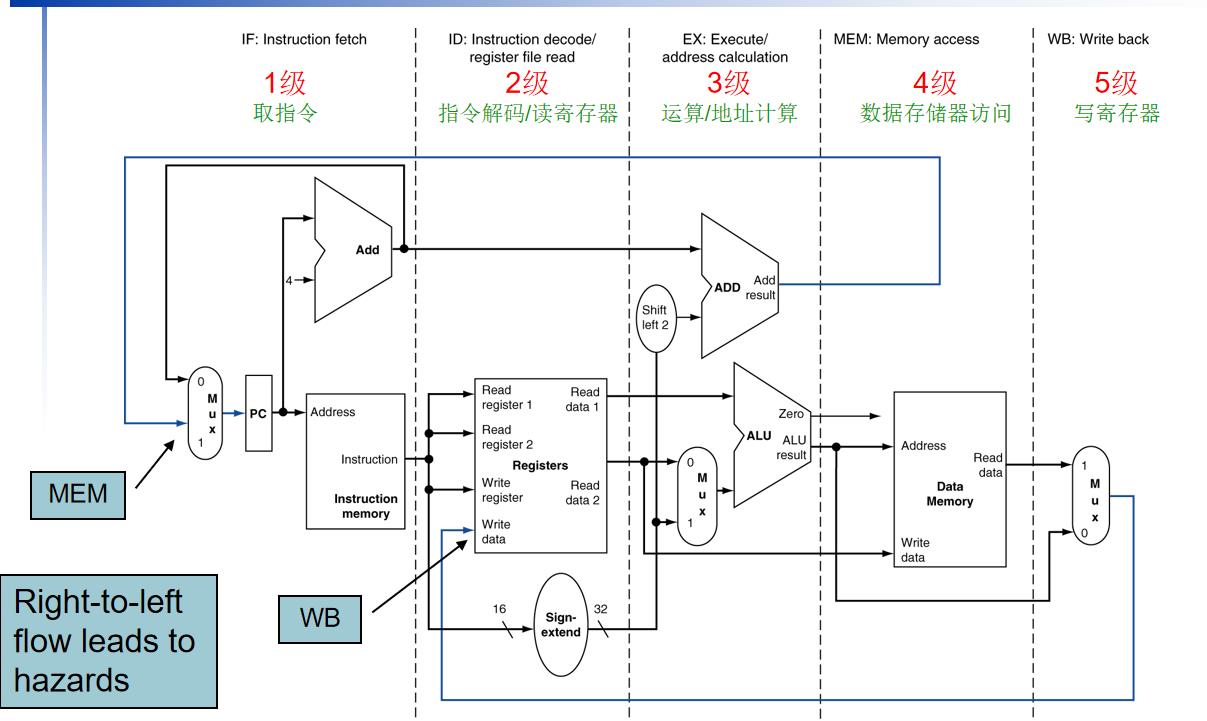

处理器

计算机的性能由指令数目、时钟周期长度和CPI决定,编译器和指令集决定了一

个程序所需要的指令数目,处理器的实现方式决定了时钟周期长度和CPI。要想

实现一个处理器,首先要构建一个数据通路,然后进一步构建一个简单的处理

器以实现MIPS这样的指令集

基本的MIPS实现

首先要设计的实现方式包含一个MIPS的核心子集

- 存储访问指令 lw sw

- 算术逻辑指令 add sub and or slt

- 分支指令 beq j

实现方式

指令的实现过程大致相同,而与具体的类型无关,前两步都是一样的

- 程序计数器指向指令所在的存储单元,并取出指令

- 根据指令内存取出一个或两个寄存器

接下来的步骤取决于具体的指令类型,每个类型的指令都大致相同,比如除了

跳转指令外所有的指令在读取寄存器后都要使用算术逻辑单元,可能用于计算

地址、执行运算或比较

逻辑设计

MIPS实现中的数据通路功能部件包括两种不同的逻辑单元:处理数据值的单元

和存储状态的单元。处理数据值的单元都是组合单元,它们的输出只决定与当

前的输入

- 组合单元 一个操作单元,如与门或ALU

- 状态单元 一个存储单元,如寄存器或存储器

建立数据通路

首先分析执行每种MIPS指令时需要哪些主要部件

- 数据通路部件 用来操作或保存处理器中数据的单元

- 程序计数器 存放下一条将要被执行指令的地址的寄存器

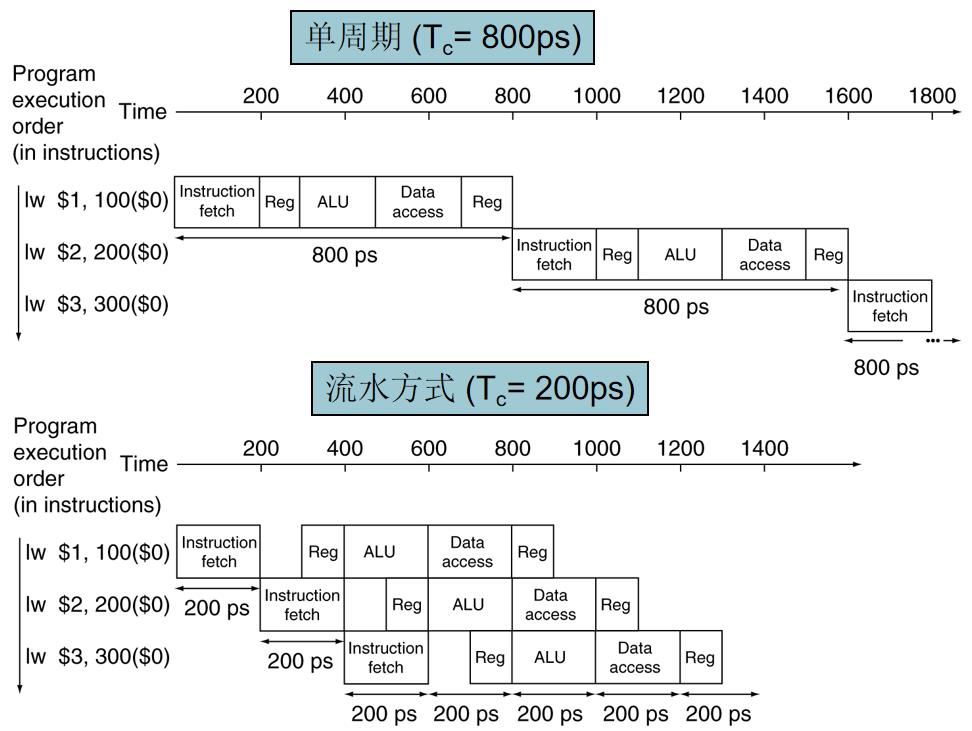

流水线

流水线是一种实现多指令重叠执行的技术

MIPS指令流水

5级, 每级完成一个操作步骤

- IF: 从内存中取指令

- ID: 指令解码& 读寄存器

- EX: 执行运算或计算地址

- MEM: 访问内存操作

- WB: 将结果写回寄存器

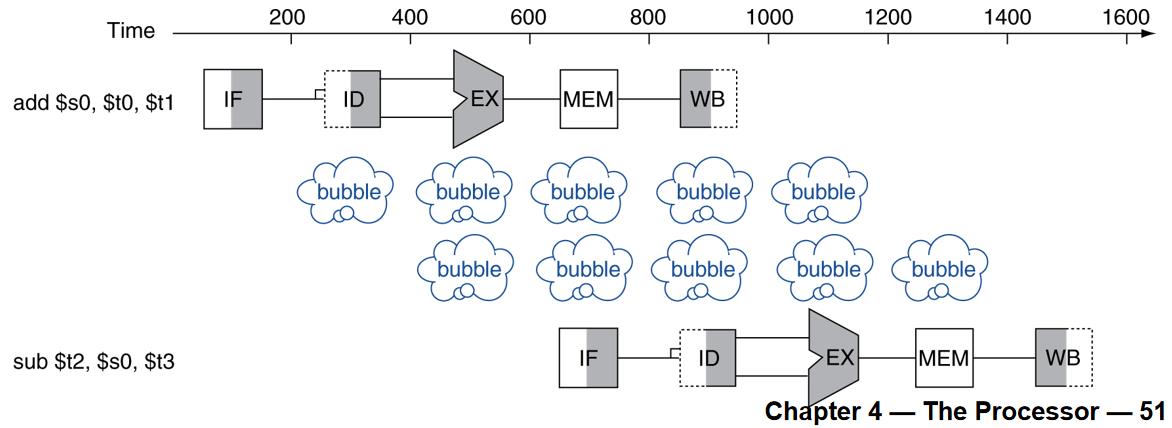

流水线冒险

冒险现象:下一周期不能按时执行下一条指令

- 结构冒险 所需的部件忙,暂不可用

- 数据冒险 需要前面某条指令的计算结果,用于本次计算输入

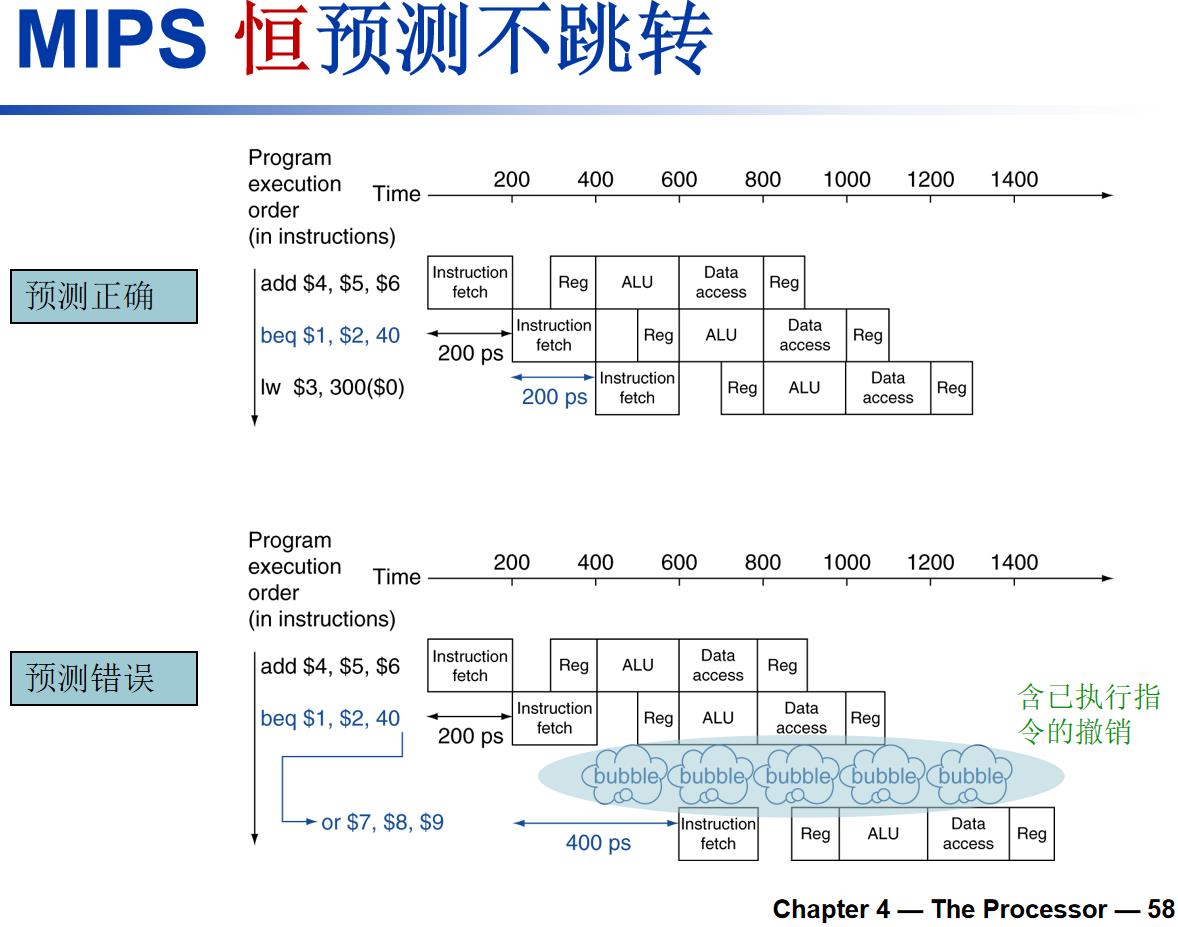

- 控制冒险 需要根据前面某条指令的结果来确定分支的选择执行

结构冒险

某个资源使用上的冲突,如果某个MIPS流水实现,且只有一个内存部件,这个

部件执行一次操作需要多个时钟周期(比如乘法器和除法器)

- 存取操作都需要访问内存

- 取指令因此而停顿

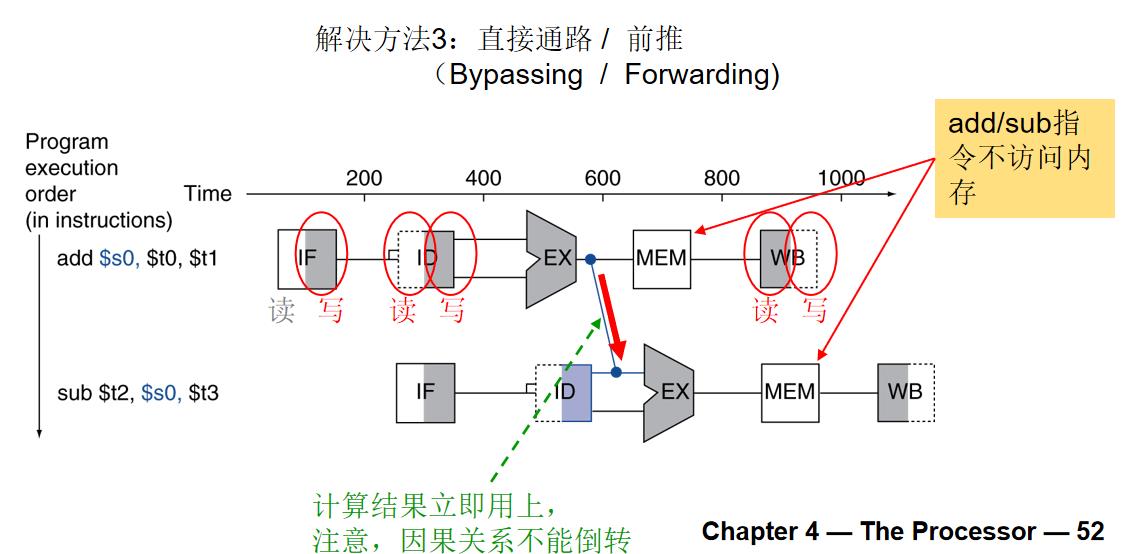

数据冒险

一条指令依赖前一条指令的执行结果

1 | add $s0,$t0,$t1 |

解决方法有三种

- 编译器安排指令序列–出现太频繁,效果不好

- 推迟执行,保持因果关系,性能下降

- forwarding 不要等待计算结果保存到目的寄存器,直接给下一条指令使用

控制冒险

下一条要取出的指令取决于分支指令的输出

数据通路